|

|

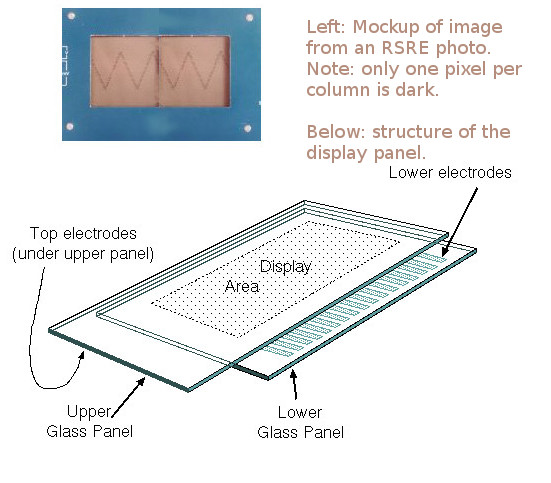

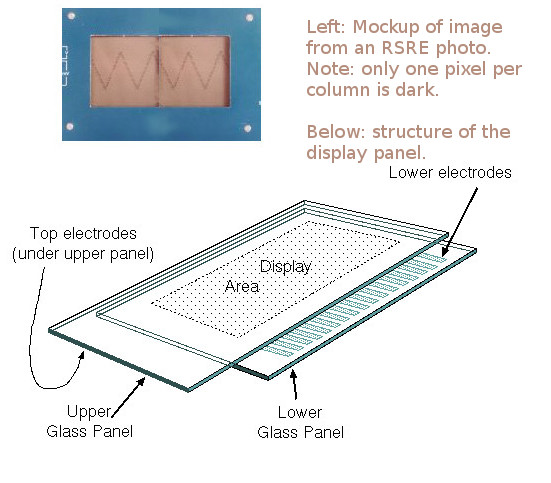

The first generation of liquid crystal displays, such as used in digital clocks and some pioneering calculators produced by Sharp, required

an electrical connection to every display element. This was unfeasible for large display panels with thousands of pixels.

The first multiplexed LCD display panels were made at RSRE (the UK's Research at the Royal Signals and Radar Establishment) and

I designed and built drive electronics for one such display.

|

|

The LED conducts electricity in only one direction: it is a diode. Unlike an LED, the LCD pixel requires

an AC voltage to alter its state and this raised very significant design challenges for scan-multiplexed display panels.

An approach was needed that exercised all of the X and Y electrodes all of the time and which delivered

waveforms that were highly anti-correlated at pixels which should be activated but which were sufficiently un-correlated at all other pixels

to keep them clear.

|

| WHAT I DID | | MODERN IMPACT |

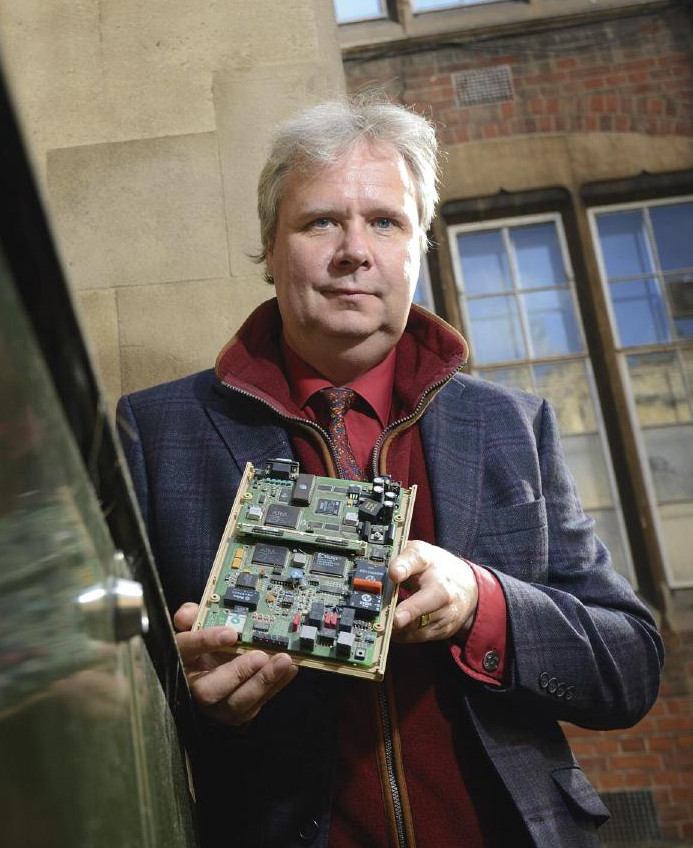

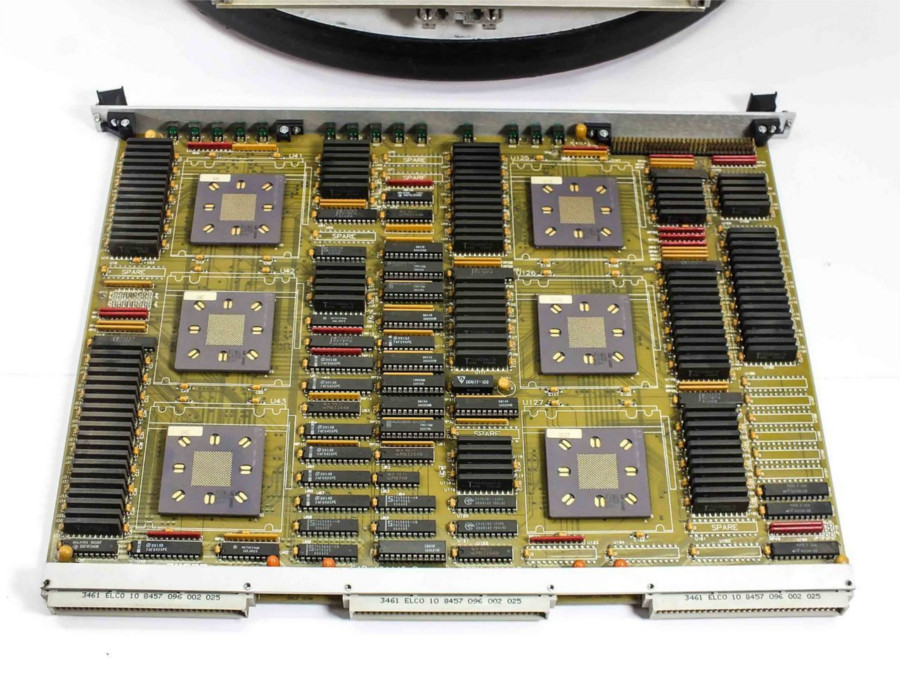

| From Prof P Raynes at RSRE, I received an LCD panel. He also sent

some elastomeric strips, which are pieces of rubber with densely-packed parallel, conductive needles.

The panel was two sheets of thin glass that had been glued together

with a small spacer between them. Close inspection revealed the nearly transparent conductive electrodes painted on the inner surfaces.

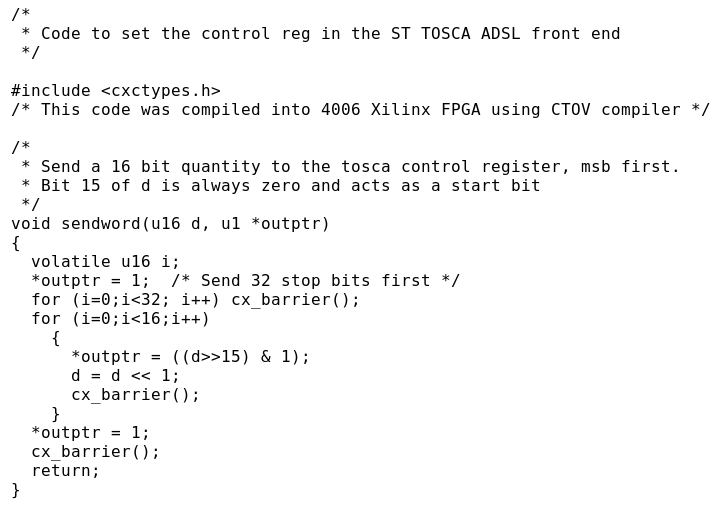

Together with my assistant Keith Barraclough (we were both interns at Plessey), I designed the PCBs to mount the delicate glass panels and

associated drive electronics. I wrote real-time software for a Z80 processor that generated the electrode waveforms.

It was then relatively trival to get one chosen pixel in every column or every row activated. This is all that is needed for graph plotting of a single line.

For more-advance plots, I generated ROM tables with various pre-computed pseudo-random sequences with known correlation patterns.

Then, with appropriate selection of waveforms, it was possible to darken more than one pixel in a row or column at once without phantoms at the transposed cross points (based on the non-transitivity of

correlation).

| |

My display had an area of about one inch by three.

As everybody knows, LCD displays became a very important technology, especially for laptops and televisions.

The LCD multiplexing problem was

never really solved. Instead, modern display panels have transistors at every pixel and so the old scan multiplexing approach can be applied.

|

|

|

|

| A mockup of the LCD display I used from an online image at RSRE. And also a schematic drawing of the panel structure. |

|

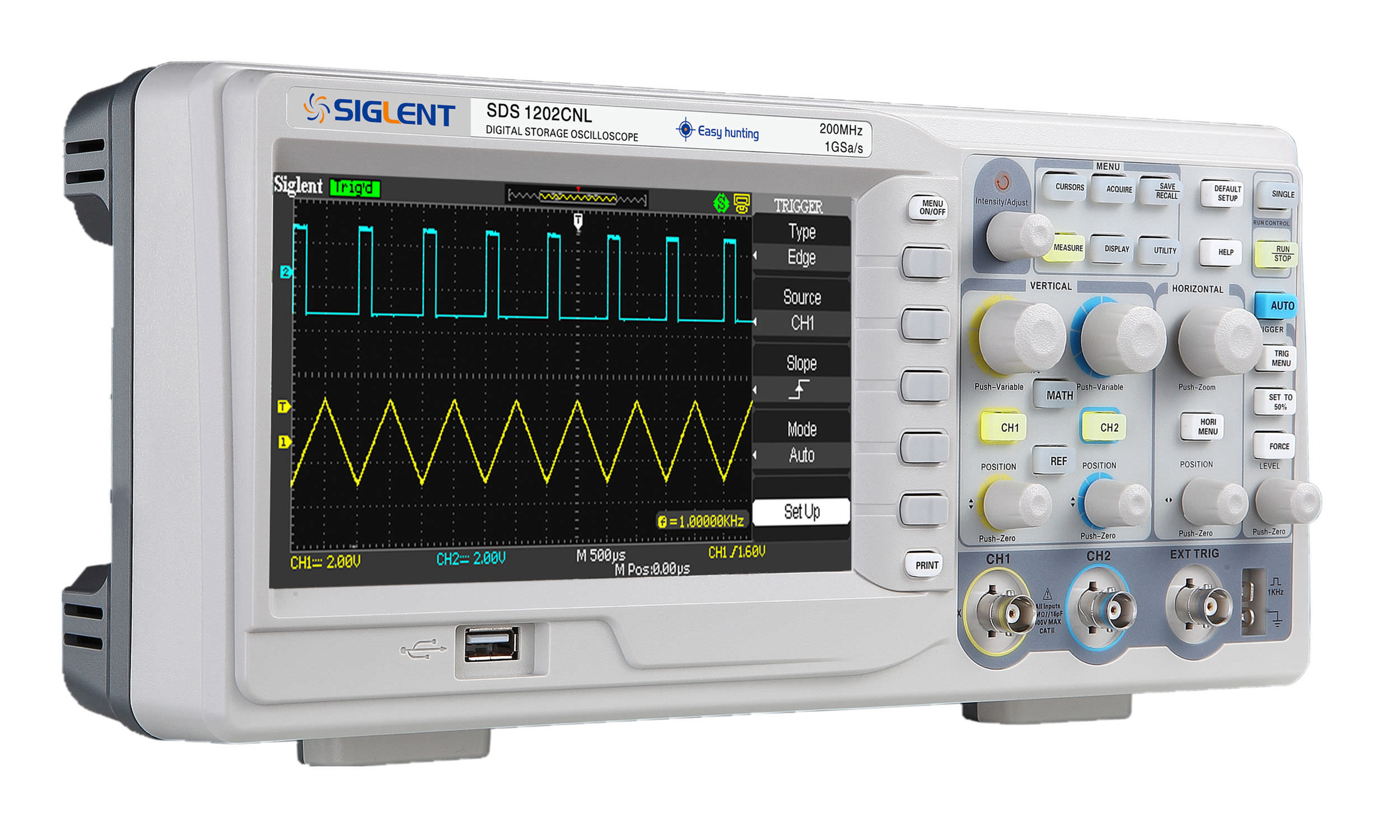

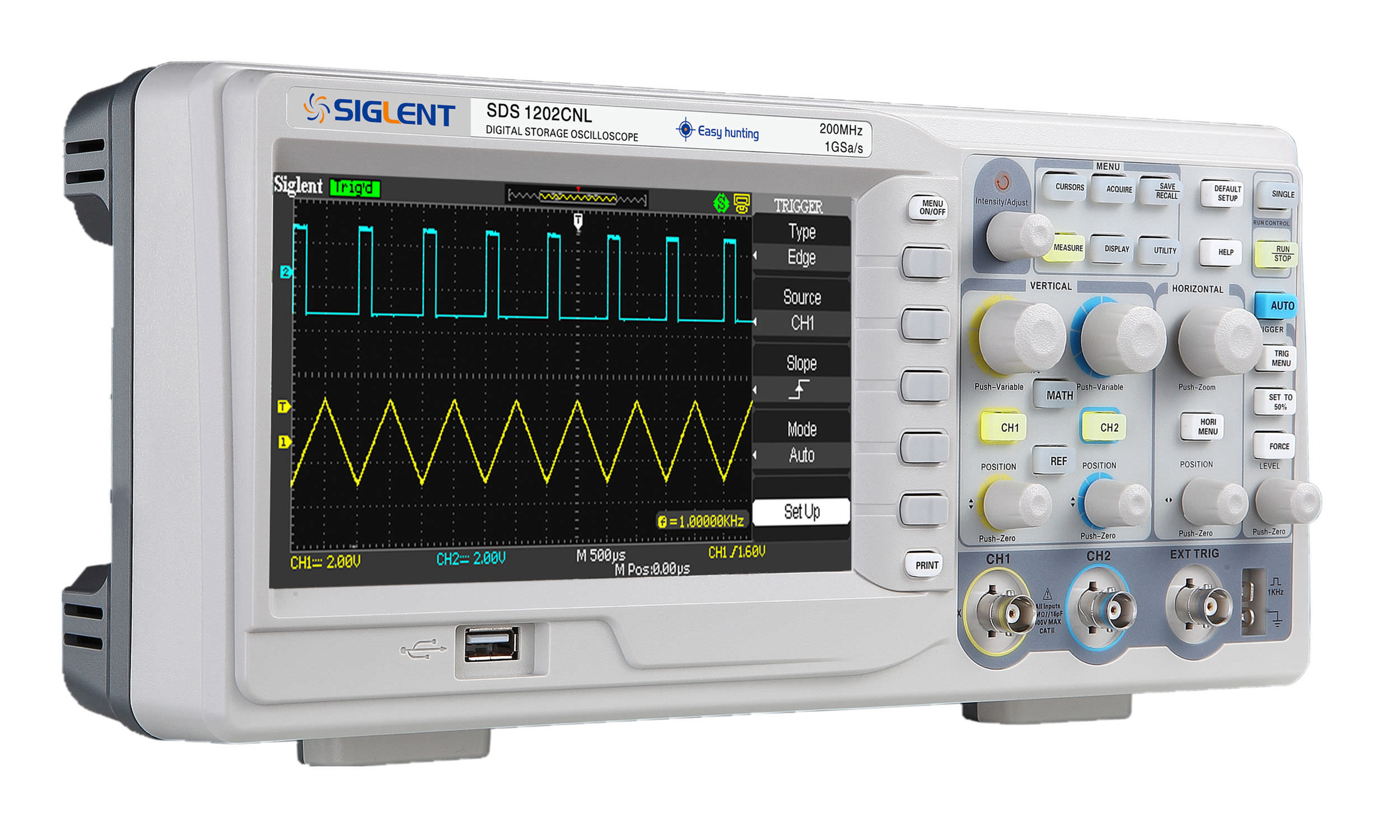

A modern LCD oscilloscope. |

|

As with quite a few technological developments conducted under the blanket of the Official Secrets Act, the UK technology

was never properly exploited. Contrary to their contracts of employment,

the good staff at RSRE did not get significant royalties from their inventions and I was told that they

ultimately sued their employer (the UK government) for failing

to maximise their benefit. I certainly did not get any money. Meanwhile, the Japanese companies Epson and Sharp took the lead.

Two or three years after this project, I saw the prototype LCD on display in the London Science Museum.

|